|

- UID

- 3495

- 帖子

- 712

- 精华

- 0

- 积分

- 2310

- 阅读权限

- 10

- 性别

- 男

- 在线时间

- 679 小时

- 注册时间

- 2006-8-3

- 最后登录

- 2016-12-19

|

118楼

发表于 2008-10-12 14:26

发表于 2008-10-12 14:26

| 只看该作者

报告备份

#include <iostream>

using namespace std;

double POWER;

const double R1=26.9;

const double R2=53.8;

const double R3=134.2;

const double Vrms= 220;

signed int select;

double function_off()

{ return POWER=0;

};

double function_weak(double p,double vrms, double r1, double r2)

{ p=vrms*vrms/(r1+r2);

return p;

};

double function_normal(double p,double vrms,double r2)

{ p=vrms*vrms/r2;

return p;

};

double function_strong(double p,double vrms, double r1, double r2,double r3)

{p=vrms*vrms/((r1+r3)*r2/(r1+r2+r3));

return p;

};

int main()

{ while(select!=4)

{cout<<" Select the switch"<<endl;

cout<<" 0. off 1. weak 2. normal 3. strong 4. close"<<endl;

cin>>select;

switch(select)

{case 0:

cout<<"The switch is off and the power is"<<" "<<function_off()<<"w"<<endl<<endl; break;

case 1:

cout<<"The wind is weak and the power is"<<" "<<function_weak(POWER,Vrms,R1,R2)<<"w."<<endl<<endl; break;

case 2:

cout<<"The wind is normal and the power is"<<" "<<function_normal(POWER,Vrms,R2)<<"w."<<endl<<endl;; break;

case 3:

cout<<"The wind is strong and the power is"<<" "<<function_strong(POWER,Vrms,R1,R2,R3)<<"w."<<endl<<endl; break;

case 4:

cout<<"You have closed the hiredrier."<<endl<<endl; break;

default:

cout<<"The range or select is from 0 to 4"<<endl<<endl; break;

}

}

}

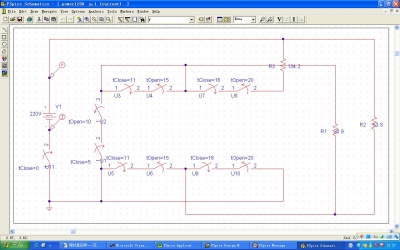

电路图

[ 本帖最后由 我是愤怒! 于 2008-10-12 15:32 编辑 ] |

-

-

未命名.JPG

(137.66 KB)

|